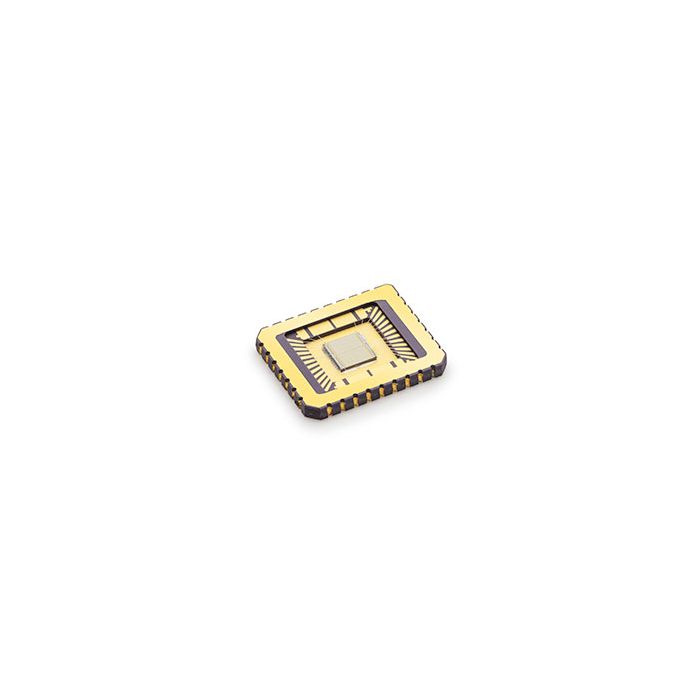

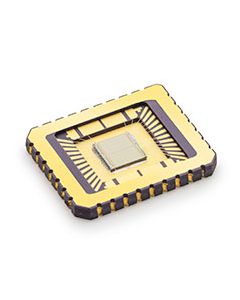

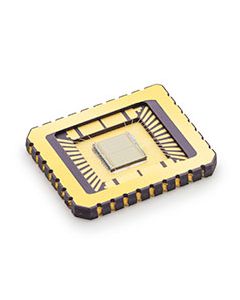

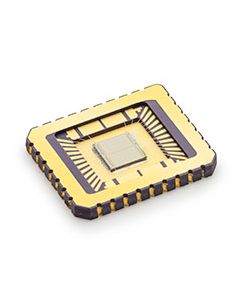

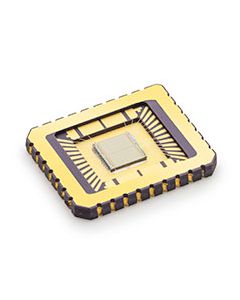

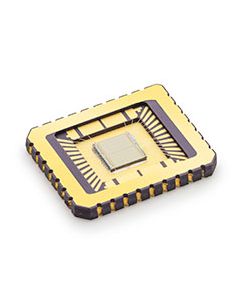

P4C174

P4C174

Pyramid Semiconductor

64K (8Kx8) CMOS SRAM with cache tag (OD)

The P4C174 is a 65,536-bit ultra high-speed cache tag static RAM organised as 8K x 8. The CMOS has equal access and cycle times. Inputs are fully TTL-compatible. The RAMs operate from a single 5V ± 10% tolerance power supply. An 8-bit data comparator with a MATCH output is included for use as an address tag comparator in high speed cache applications. The reset function provides the capability to reset all memory locations to a LOW level.

The MATCH output of the P4C174 reflects the comparison result between the 8-bit data on the I/O pins and the addressed memory location. 8K cache lines can be mapped into 1M-Byte address spaces by comparing 20 address bits organised as 13-line address bits and 7 page address bits.

Low power operation of the P4C174 is enhanced by automatic powerdown when the memory is deselected or during long cycles times. Also, data retention is maintained down to Vcc=2.0. Typical battery backup applications consume only 30 µA at Vcc=3.0

Click below to request a quote for this item. Or for product advice, stock and lead time enquiries call our team on 0330 313 3220.

| Attribute | Value |

|---|---|

| Key Features |

|

| TAA (ns) | 15/20/25 |

| DIP | 28 |

| Qualified To | MIL-STD-883 |

| Size | 64K |

| Attribute | Value |

|---|---|

| Data Sheet | Click here to view |