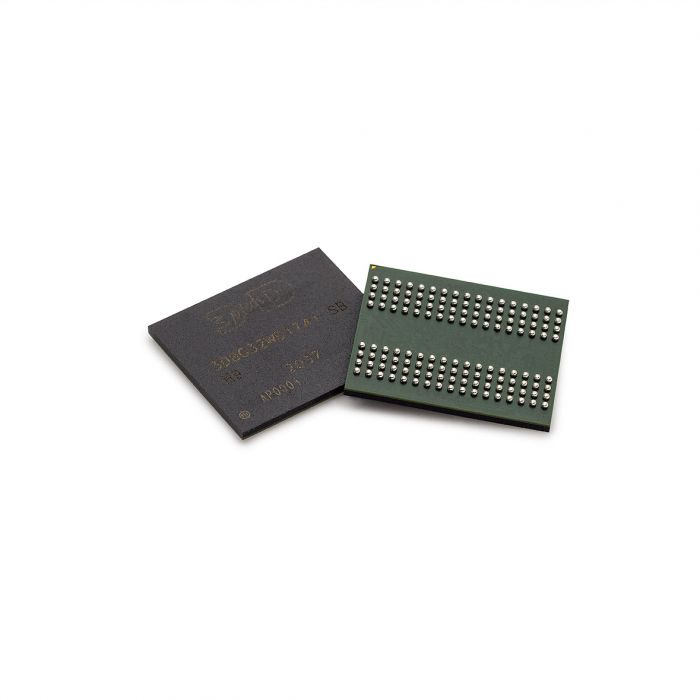

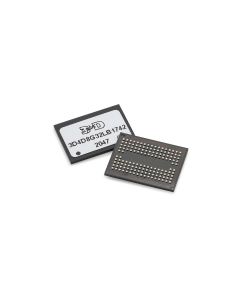

3D3D8G32WB1741

3D3D8G32WB1741

3D Plus

1.5V, 8Gb DDR3 SDRAM organised as 256Mx32

The 3D3D8G32WB1741 / 3D3D8G32YB1741 is a high speed stack multi-chip package integrated 4Gbits x 2 DDR3 SDRAM and fabricated with ultra high performance CMOS process containing 8 Gbits which is organised as 32Mbits x 8 banks by 32 bits.

This synchronous device achieves a high speed double-data-rate transfer rates of up to 1600 Mb/sec/pin (DDR3-1600) for general applications. The chip is designed to comply with the following key DDR3 SDRAM features: (1) posted CAS by programmable additive latency, (2) On Die Termination (3) programmable driver strength data,(4) clock rate of 1600Mbps. All the control and address inputs are synchronised with a pair of externally supplied differential clocks.

Inputs are latched at the cross point of differential clocks (CK rising and /CK falling). All I/Os are synchronised with a pair of bidirectional differential data strobes (DQS and /DQS) in a source synchronous fashion. The address bus is used to convey row, column and bank address information in a /RAS and /CAS multiplexing style. The 8Gb DDR3 devices operates with a single power supply: 1.35V or 1.5V for VDD and VDDQ. This device is ideal for high density memory applications that require high speed transfer and compatibility with standard servers and networking equipment.

Click below to request a quote for this item. Or for product advice, stock and lead time enquiries call our team on 0330 313 3220.

| Attribute | Value |

|---|---|

| Product Type | DDR3 SDRAM |

| Data_Sheet |

To request a datasheet, contact a member of our high-reliability team [email protected] |

| Configuration | 256M x32 |

| Package | FBGA 136 |

| Temperature Range |

|

| Power Supply | 1.35V or 1.5V |

| Features |

|

| Attribute | Value |

|---|---|

| Data Sheet | Click here to view |