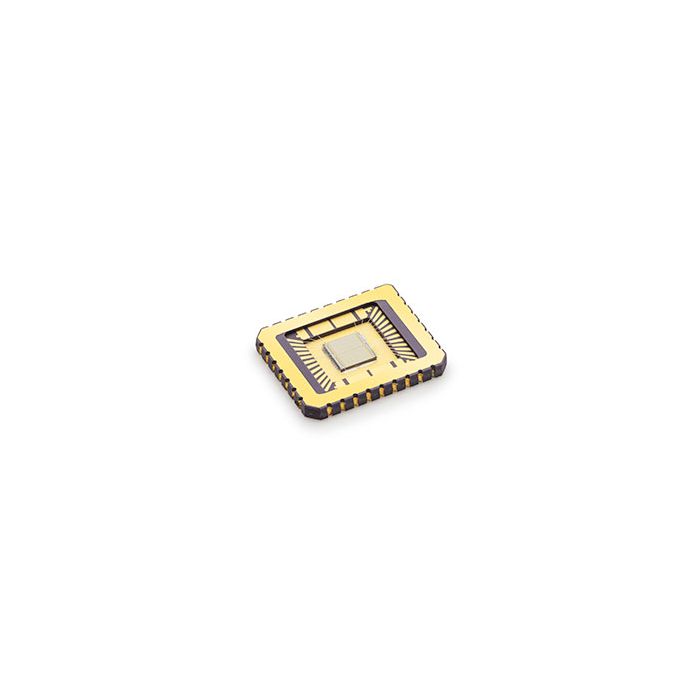

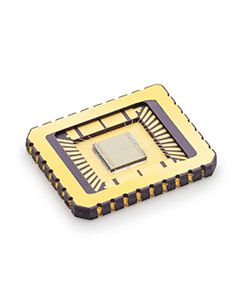

P4C1256L

P4C1256L

Pyramid Semiconductor

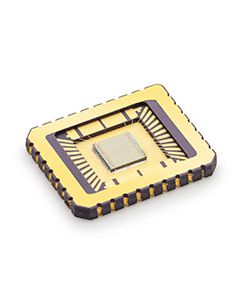

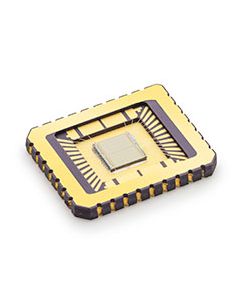

256K (32Kx8) CMOS SRAM, 5V

The P4C1256L/LL is an asynchronous 262,144-bit low power CMOS static RAM organised as 32K x 8. The CMOS memory require no clocks or refreshing and has equal access and cycle times. Inputs are fully TTL-compatible. The RAM operates from a single 5V ± 10% tolerance power supply.

Access times of 55 ns and 70 ns are available. CMOS is used to reduce power consumption to a low level.

Memory locations are specified on address pins A0 to A14. Reading is accomplished by device selection (CE) and output enabling (OE) while write enable (WE) remains HIGH. By presenting the address under these conditions, the data in the addressed memory location is presented on the data input/output pins. The input/output pins stay in the HIGH Z state when either CE or OE is HIGH or WE is LOW.

The P4C1256LL device is a very low power version.

Click below to request a quote for this item. Or for product advice, stock and lead time enquiries call our team on 0330 313 3220.

| Attribute | Value |

|---|---|

| Key Features |

|

| Standard Military Drawing Number(s) | SMD 5962-88552 |

| TAA (ns) | 20/25/35/45/55/70 |

| DIP | 28 |

| LCC | 28/32 |

| FP | 28 |

| Qualified To | MIL-STD-883 |

| Size | 256K |

| Attribute | Value |

|---|---|

| Data Sheet | Click here to view |